请注意,本文编写于 150 天前,最后修改于 150 天前,其中某些信息可能已经过时。

目录

SRAM

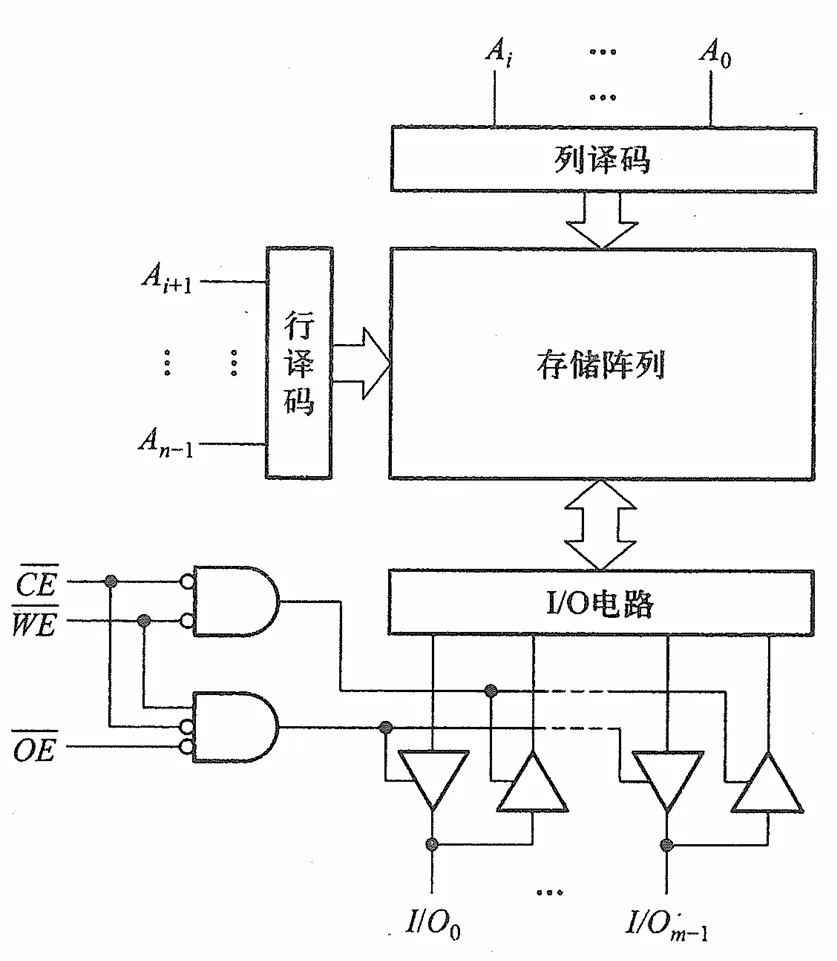

SRAM中的每个存储单元相当于一个锁存器,它由存储阵列,地址译码器和输入输出控制电路三部分组成

其中是根地址线,一个特定的地址保存着位二进制数,输入输入由根双向数据线负责。是输出使能,是写使能。另有片选信号,只有激活片选信号时SRAM才能进行IO操作,否则三态缓冲器都为高阻态

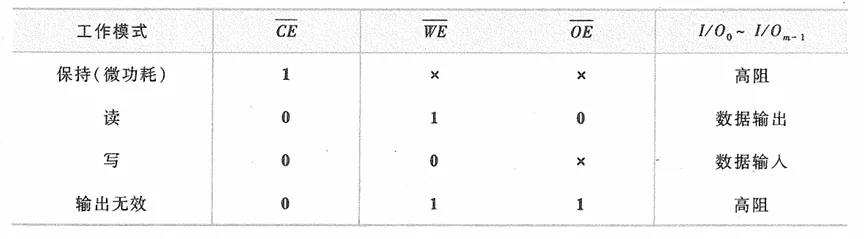

SRAM存储单元

SRAM存储单元由6个MOS管组成

另外有两个MOS管控制数据线,它们是多个存储单元共用的。其中形成两个CMOS反相器,进而构成一个锁存器,控制行选择线,控制列选择线

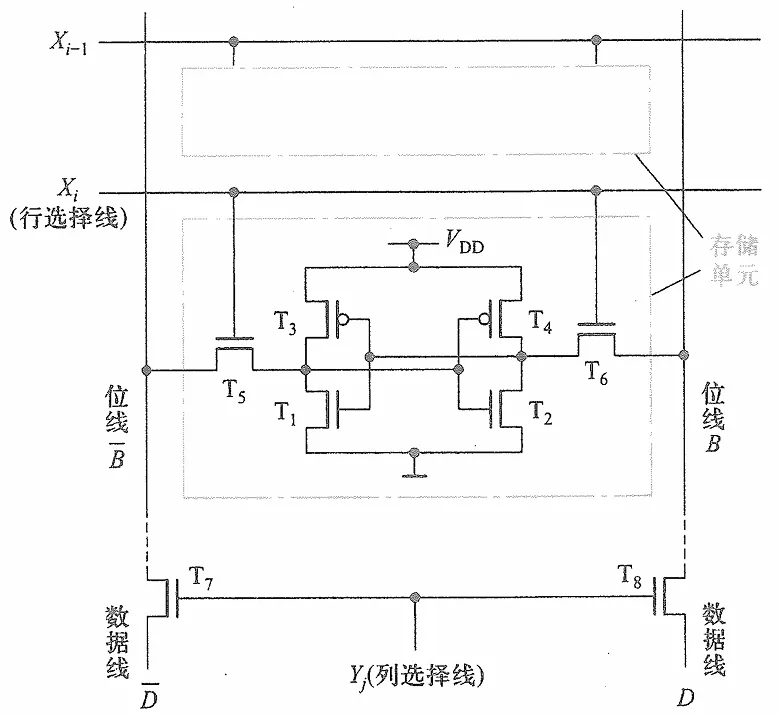

同步SRAM

上一节的SRAM没有时钟信号,可以在任意时刻进行读写。加入了时钟的SRAM称为同步SRAM,除输出使能外,所有的输入都在时钟上升沿被采样

值得注意的是丛发模式,当ADV被置为1时,地址寄存器不再接受新的地址,地址的低位由丛发控制器自行产生,从而可以读写多个连续地址的数据

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

目录