目录

二进制计数器

按照自然二进制数递增或递减编码的计数器称为二进制计数器,N位二进制计数器的模为

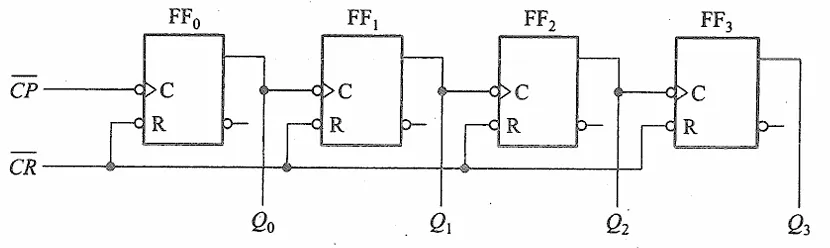

一个简单的实现方式是异步,由N个在时钟上升沿翻转的触发器串联构成

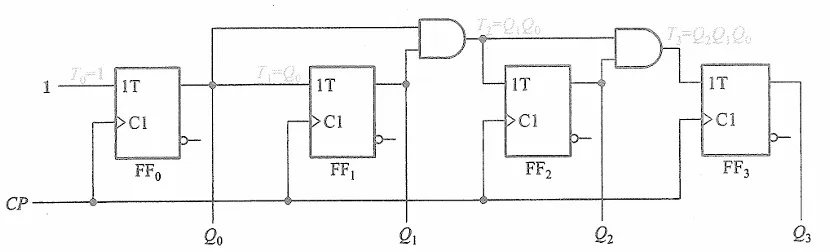

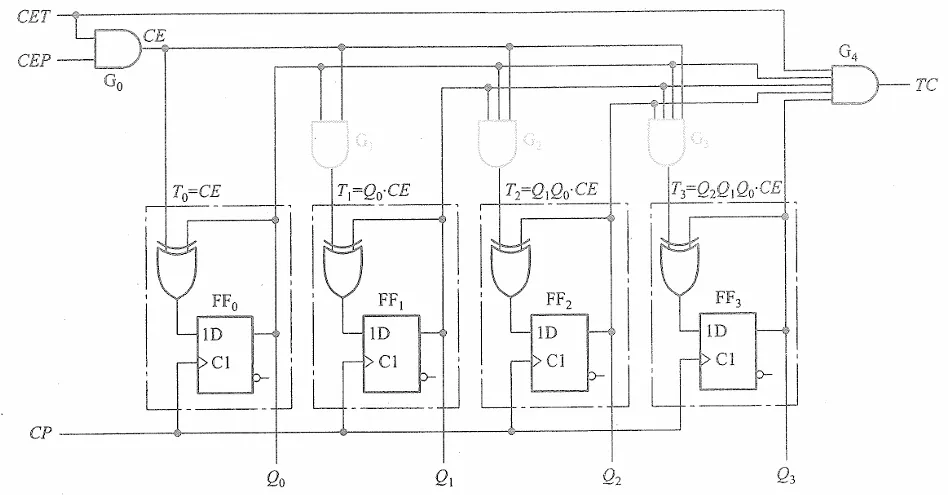

不过由于异步的延时,当时钟频率过高时会出现问题。需要同步二进制计数器,鉴于计数器翻转的特性,使用T触发器是较为简单的。假定计数器的低位到高位依次为

那么每次都翻转,在为1时翻转,在都为1时翻转...那么就可以得到激励方程

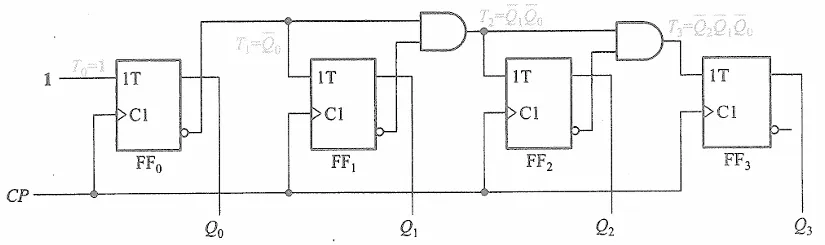

若是递减计数器,每一位在其低位都为0时翻转,即激励方程为

那么可以据此得到逻辑图。递增计数器如下

递减计数器如下,只是都接到了反上

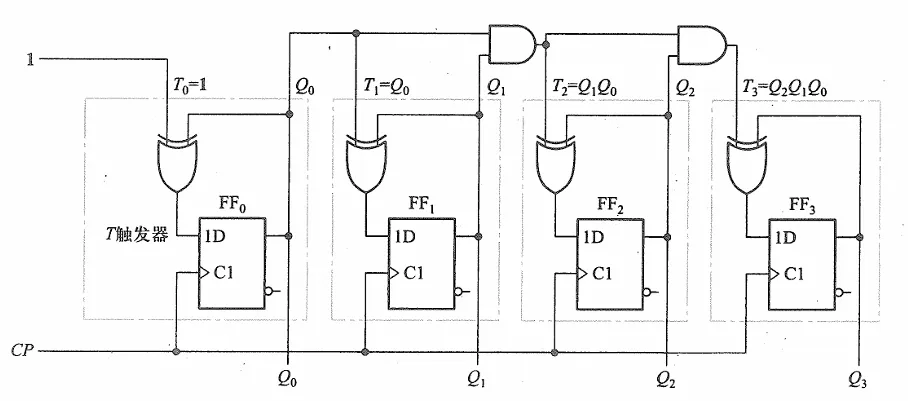

同步计数器的更新延迟都是一个触发器延迟,比异步计数器稳定得多。可以将T触发器换成等价的D触发器结构

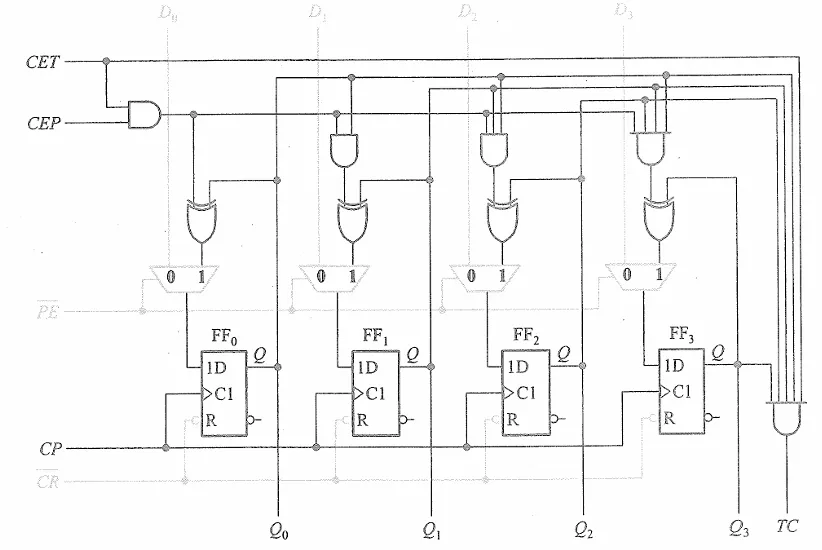

为了功能更加完善,可以添加进位,也就是当前状态全是1时需要进位。由于是同步电路,状态变成全1在时钟上升沿后,需要在下一次上升沿到来前将进位置为1.另外添加直接进位允许信号CET和片内进位允许信号CEP,它们都为1是计数器才计数,否则保持。逻辑图就像这样

完善的计数器还需要异步清零与同步并行置数功能,也就是需要一个优先级最高的清零和输入的手段。清零可以利用D触发器的清零实现,置数则可以使用二选一数据选择器,从递增的数和输入中选取一个。逻辑图如下

其他模数的计数器

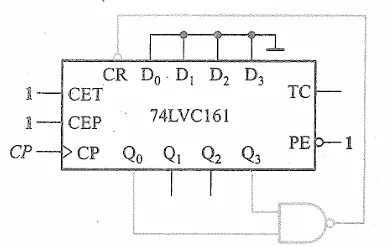

可以以的计数器为基础,得到其他模数的计数器。如果计数器提供了异步清零功能,则可以将特定的输出口做与运算接入清零端。这样在达到指定计数后清零就会被置为1,下一次时钟脉冲到来后计数将会变为全零,此时清零信号重新变为0,计数循环再次开始。就像这样,称为反馈清零法

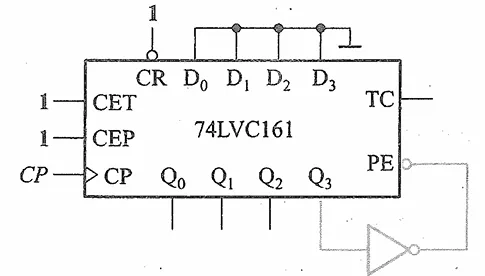

如果计数器有置数功能,则可以像这样

在计数达到指定值后,置数信号变为1,在下一次时钟脉冲到来时,计数器变为置数端输入的数,然后置数信号变为0,重新开始计数循环

计数器的级联

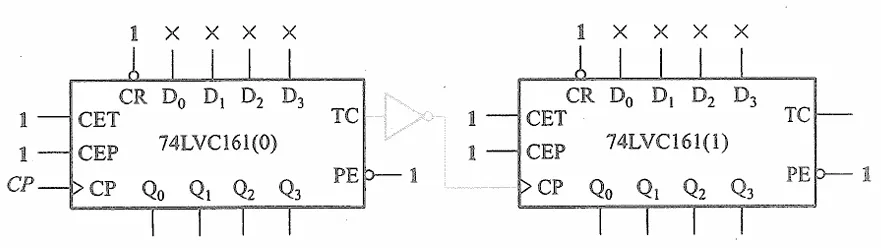

一种简单的方法是异步级联,将上一级计数器进位信号的反接到下一级计数器的时钟信号上,这样当上一级计满(全1)即将跳为全0时,进位信号变为1,其反变为0;当它从全1跳为全0时,进位信号的反由0跳1,使得下一级计数器加一。逻辑图就像这样

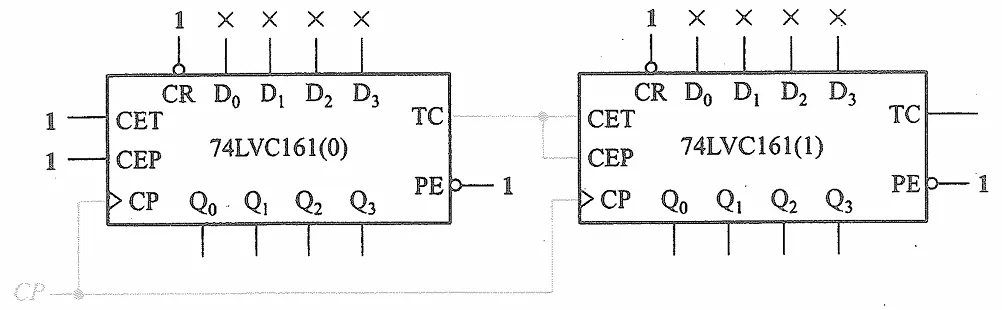

这样级联较多会带来较大延迟,那么就可以采取同步级联的方式。将上一级计数器的进位信号接到下一级计数器的使能上,只有上一级将要进位时才允许下一级计数。就像这样

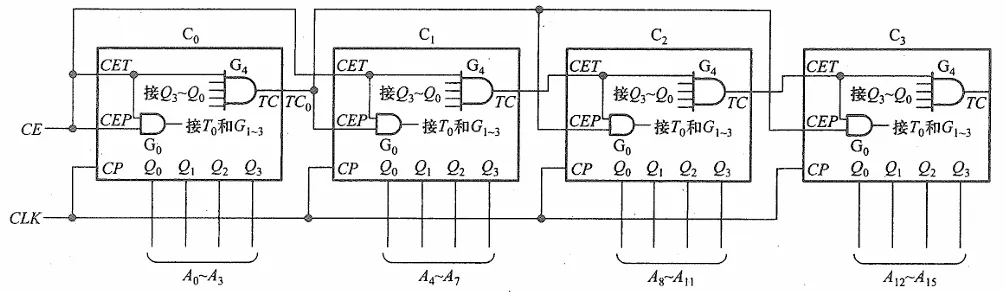

不过只有当所有低位都进位时才允许高位进位,这样级数越多就需要越多输入端的与门,增加电路的复杂度。此时就可以采用同步异步结合的方式,就像这样

其中的进位信号同步传递给后面的三个计数器,后面三个计数器的进位信号则是从前往后依次传递的。这样兼顾了进位延迟与电路复杂度

环形计数器

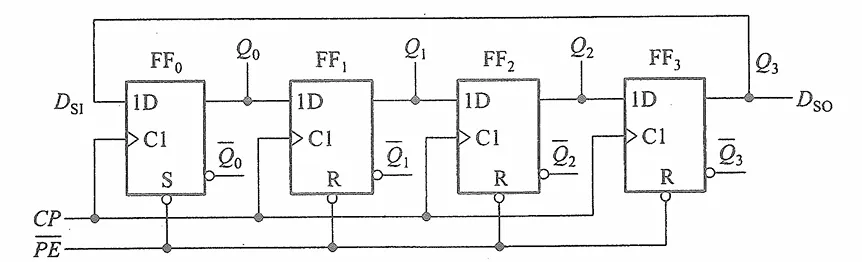

将计数器的末尾连接到开头形成环形计数器

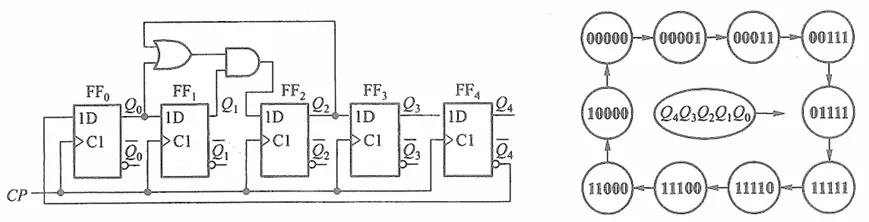

如果事先将计数器置为0001,则计数器的输出在四个状态中循环,构成模4计数器。不过这样状态利用率不高,如果将最后一个触发器的反接到开头,则形成扭环形计数器。5个触发器构成的模10扭环形计数器如下

由于每一个时钟上升沿只有一个触发器改变状态,所有不会出现竞争冒险

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!