目录

数据选择器

数据选择器有数据输入端和地址输入端,根据地址将某个数据输入端上的信号接到输出上

二选一数据选择器与其扩展

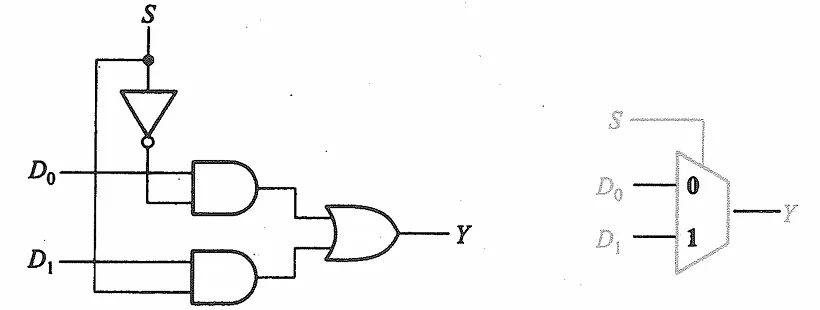

二选一数据选择器在两个数据输入中选择一个输出,记数据输入为,地址输入为,则其输出的逻辑函数式可以写为

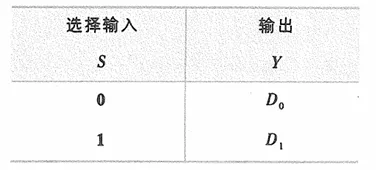

真值表为

依此给出其逻辑电路,逻辑符号简化为右侧

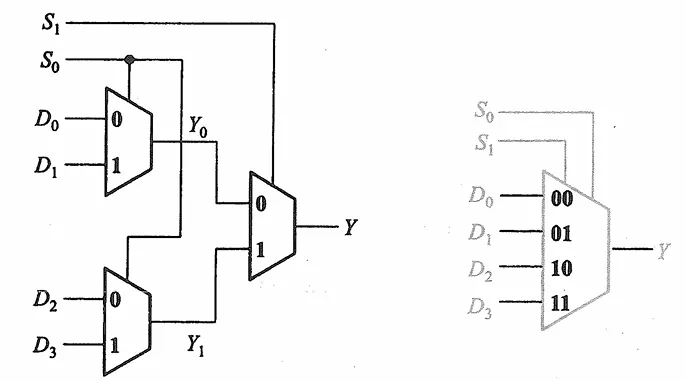

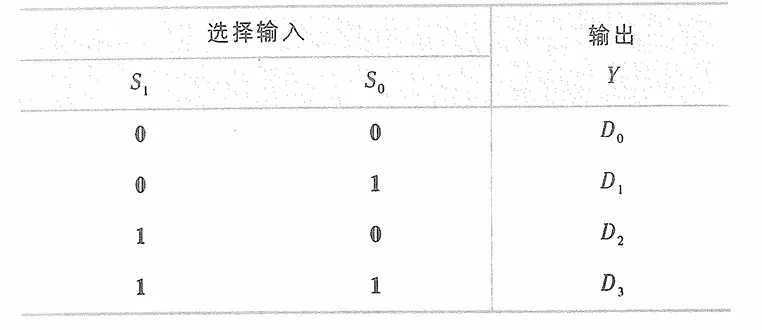

可以用三个二选一数据选择器扩展为一个四选二数据选择器,想法是用一个数据选择选择两个数据选择器中的一个,再由下一级的数据选择器选择数据

其真值表如下

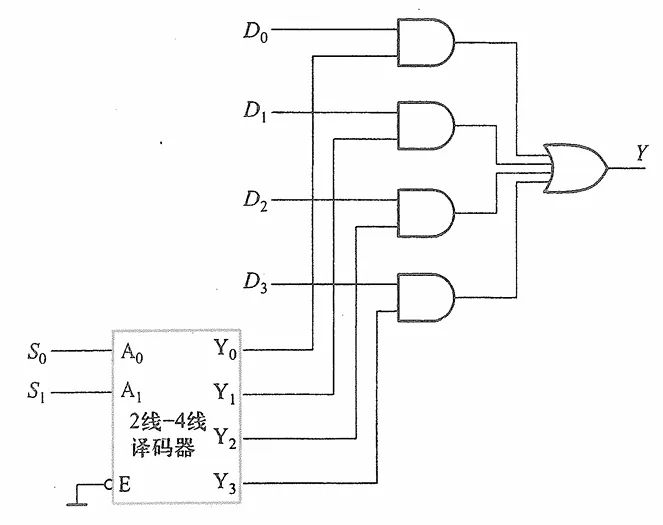

也可以使用译码器和与门或门构成数据选择器,如下面的四选一数据选择器

译码器通过控制与门的输出进而选择数据

数据选择器实现逻辑函数

任意的逻辑函数都可以写为最小项求和的形式,如

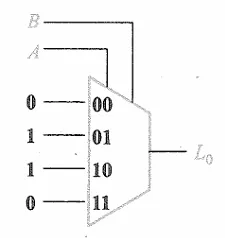

就可以用数据选择器实现为

不过在变量数目增加的时候数据选择器的线数会指数增加,这不好。不过数据选择器的数据不是非得接0或是1,也可以接逻辑函数,如

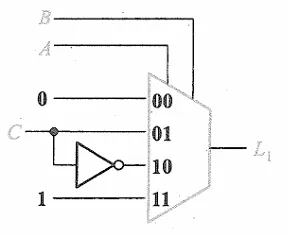

它就可以用四选一数据选择器实现为

还可以进一步使用二选一数据选择器实现

这样的逻辑表达式是利用香农展开定理得到的

香农展开定理

任何一个逻辑函数都可以被分解为

那么逻辑函数用香农展开定理对展开得到

不过用展开会更加简单

实际使用时应当选择最简单的展开方式

查找表LUT

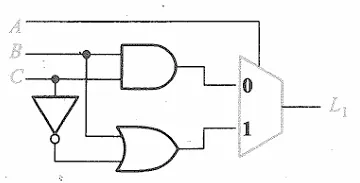

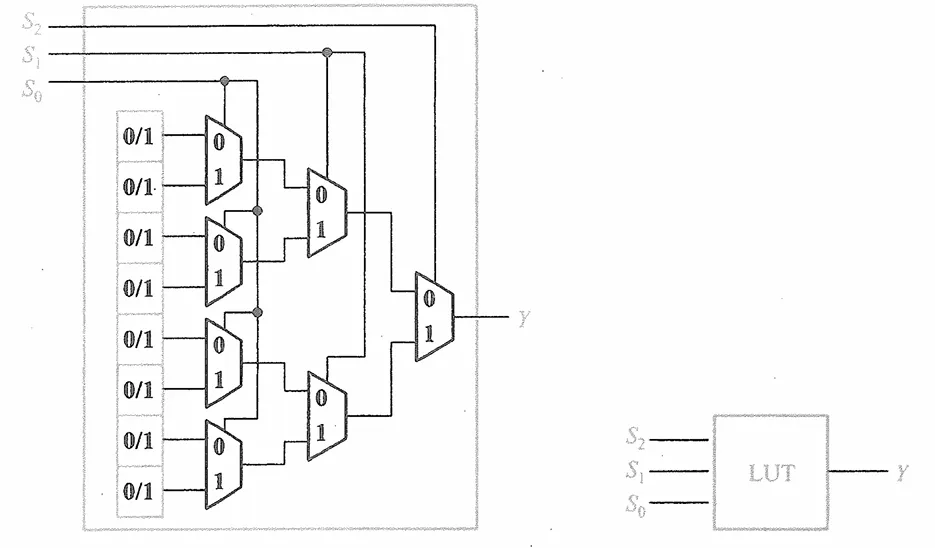

LUT是一个以真值表形式实现的逻辑函数,3输入的LUT可以这样由数据选择器实现

LUT是构成FPGA的基本单元

移位器

移位器是能将一串二进制数进行左移或者右移操作的逻辑器件

基本移位器

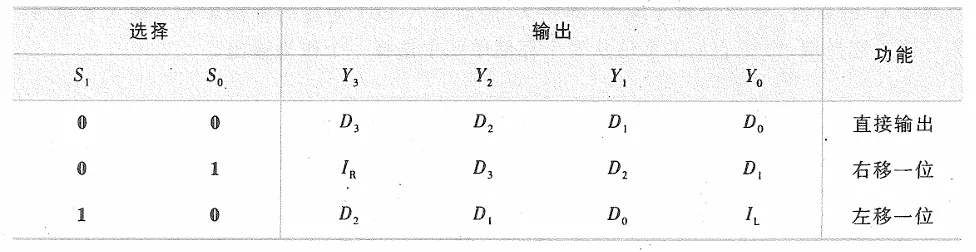

4位基本移位器的功能表如下

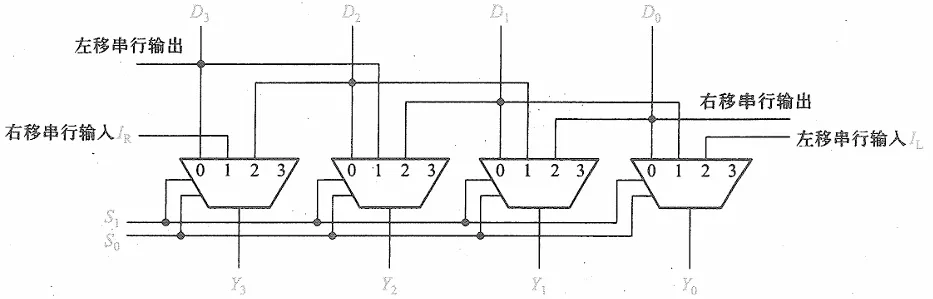

它可以由数据选择器实现

每一个数据选择器根据输入选择输出左边的数据还是自己的数据或是右边的数据

桶型移位器

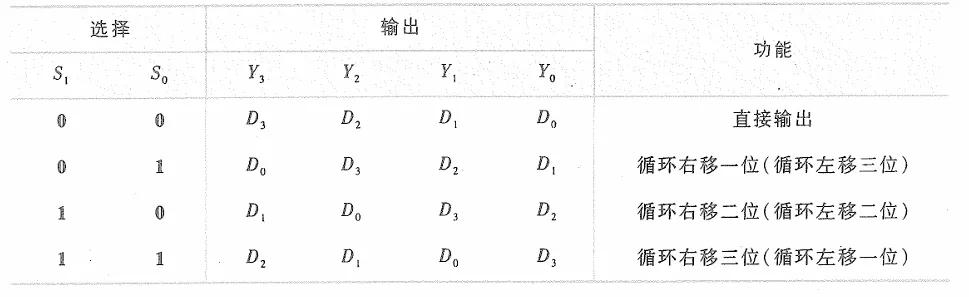

桶型移位器不接受左边输入与右边输入,而是采取循环移位,并且可以移动任意多位。4位桶型移位器的功能表是这样的

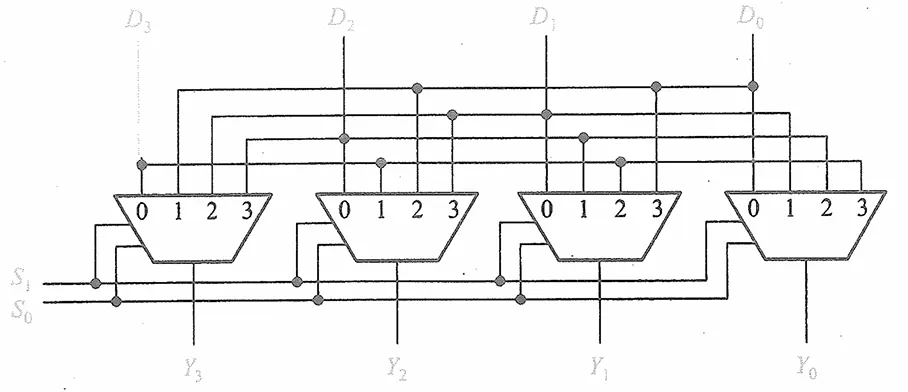

它可以由数据选择器实现

每个数据选择器根据移位的不同选择某一位进行输出,因而位桶型移位器需要个选1数据选择器

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!