请注意,本文编写于 151 天前,最后修改于 151 天前,其中某些信息可能已经过时。

目录

设计的一般步骤

- 由给定的逻辑建立原始状态图和原始状态表

- 化简状态

- 状态分配

- 选择触发器

- 确定激励方程组和输出方程组

- 画出逻辑图并检查自校正能力

首先分析问题,将其转换为原始状态转换图与原始状态转换表。这样原始的东西可能含有多余的状态,如果两个状态在相同的输入下有

- 次态相同

- 输出相同

那么它们就是等价的状态,可以合并为一个。将两个等价状态合并为一个不会改变输入输出关系

然后为每个状态指定一个特定的二进制代码,然后根据状态的数目确定触发器的数目。假定状态数目为,则触发器数目应满足

采用格雷码可以降低竞争冒险的产生,并且触发器翻转次数少,功耗低

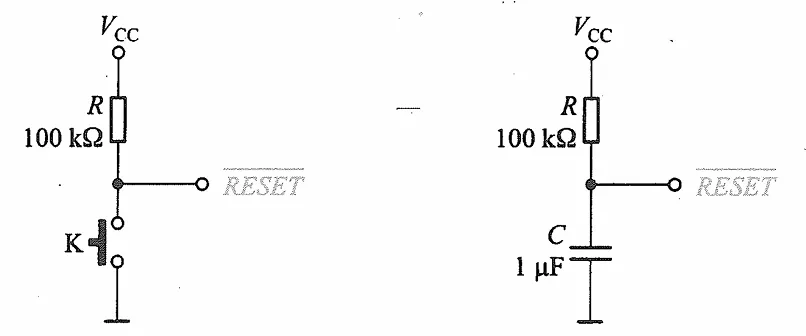

有些电路会有无效状态,可能会陷入无效状态不能退出。如果不能自校正则应修改设计。若电路要求从指定的初始状态工作,则可以采用触发器的直接置0置1功能,配合手动复位电路或是上电自动复位电路

8421BCD计数器

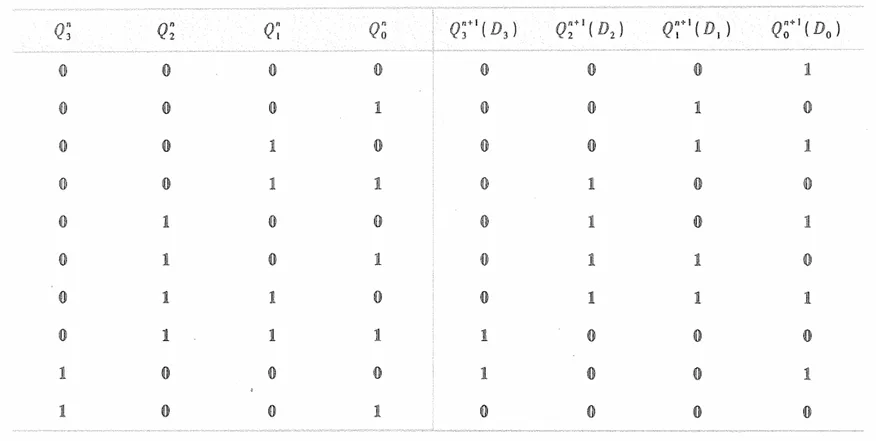

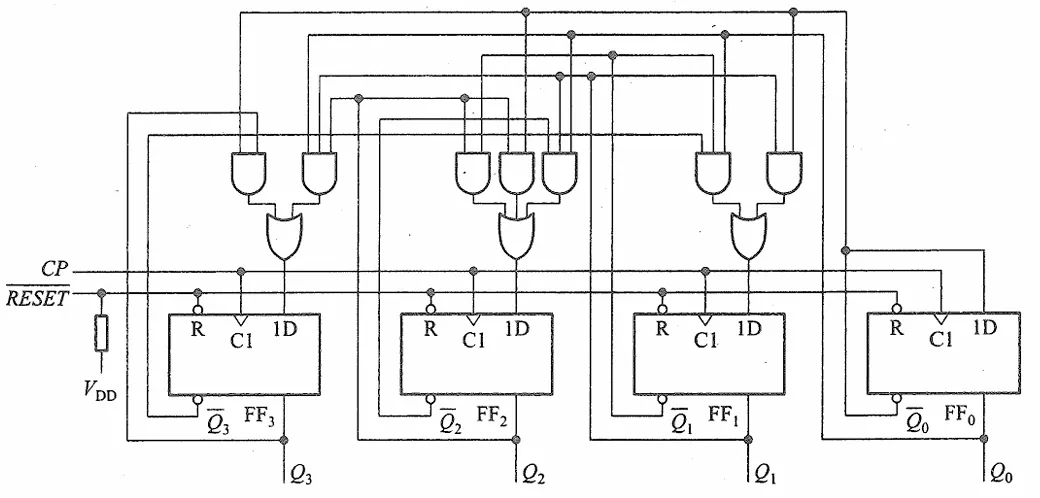

每一个时钟脉冲对计数器状态+1,从0000到1001共10个状态,需要个D触发器,将激励信号一同列入状态转换表

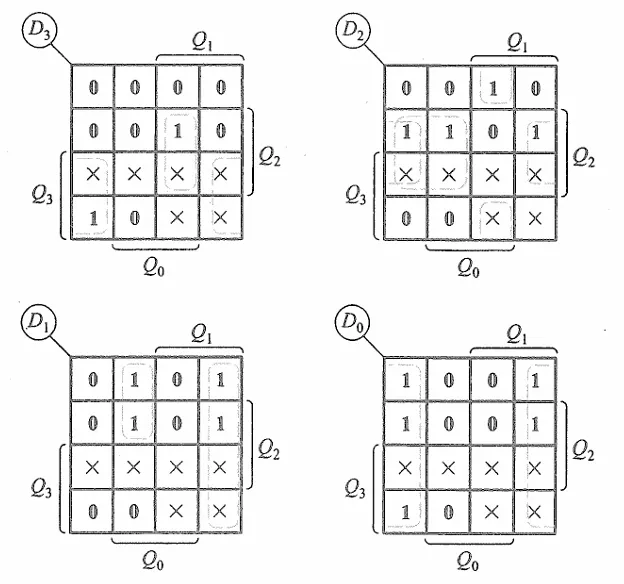

由此给出卡诺图

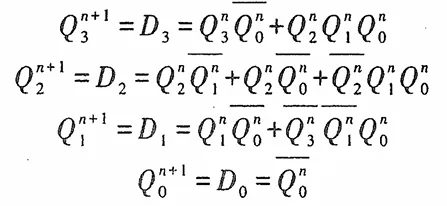

进而化简得到激励方程组

它同时也就是状态转换方程组(恰好)。进而就可以得到逻辑图

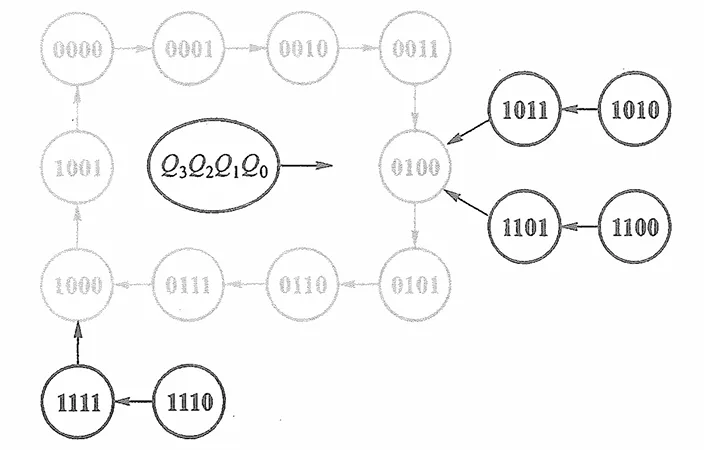

检验自校正能力:6个无效状态都能自动变为有效状态,状态转换图如下

时钟偏移

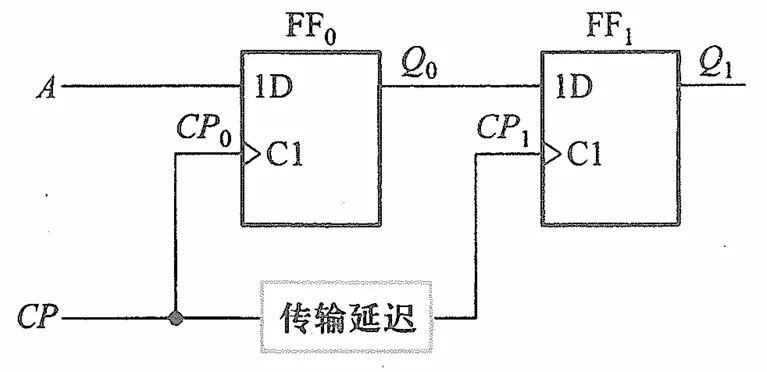

电路规模较大时,每个触发器的时钟信号线长度可能存在较大差异,使得时钟边沿到来的时间可能会存在延迟。如果这个延迟大于触发器本身的延迟,会使得以该时刻状态为输入的触发器收到了更新后的状态,进而引发错误。如

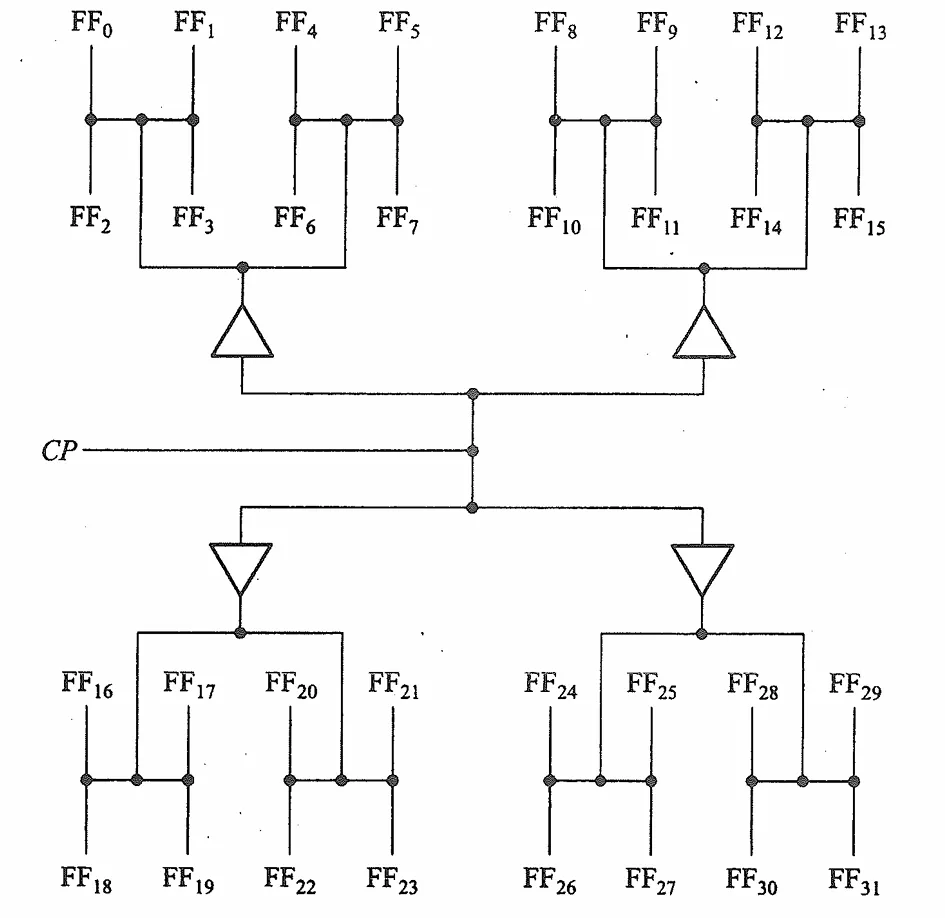

出现时钟偏移的原因可以归纳为

- 各触发器时钟传输路径长度不同

- 各触发器时钟传输路径上的缓冲器数目不同

- 各触发器时钟传输路径上的负载不平衡(特别是容性负载)

使用H型时钟布线可以有效减小时钟偏移

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

目录