请注意,本文编写于 151 天前,最后修改于 151 天前,其中某些信息可能已经过时。

目录

时序电路的基本结构

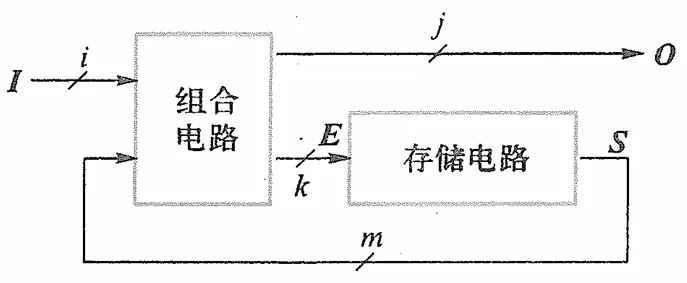

时序逻辑电路由组合电路(完成逻辑运算)和存储电路(记忆功能),可以画成这样

其中

- 是输入信号

- 是输出信号

- 是状态信号,也称为状态变量,表示时序电路当前的状态

- 是激励信号,驱动存储电路转换为下一状态

描述它们的关系需要三个方程:激励方程组,状态转换方程组,输出方程组

因而时序电路是状态依赖的,称为状态机。状态数有限的状态机称为有限状态机

异步与同步电路

如果时序电路中触发器的时钟输入没有连接在统一的时钟脉冲上,则状态更新不是同时的,即异步时序电路。如果由触发器构成则为脉冲异步时序电路,如果由锁存器构成则为电平异步时序电路

同步时序电路中存储电路状态的转换是在同一时钟脉冲源的同一边沿作用下同步的

米利型和穆尔型时序电路

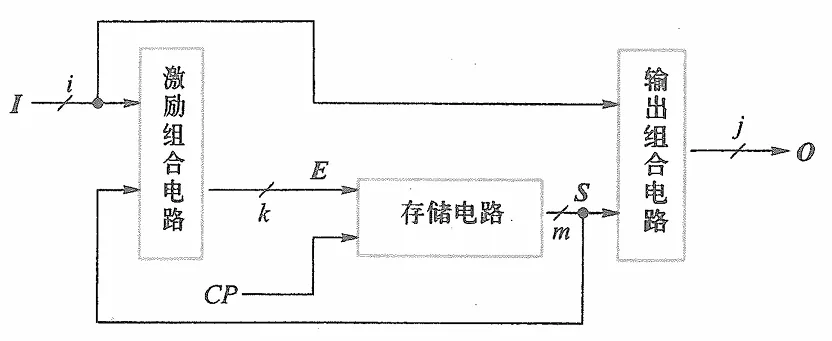

将组合逻辑电路拆为激励组合电路与输出组合电路两部分。如果输出信号与输入变量有关,即

那么电路在非时钟有效沿期间输出信号可能会随输入信号变化,不能始终保持输出信号与时钟同步,称为米利型,像是这样

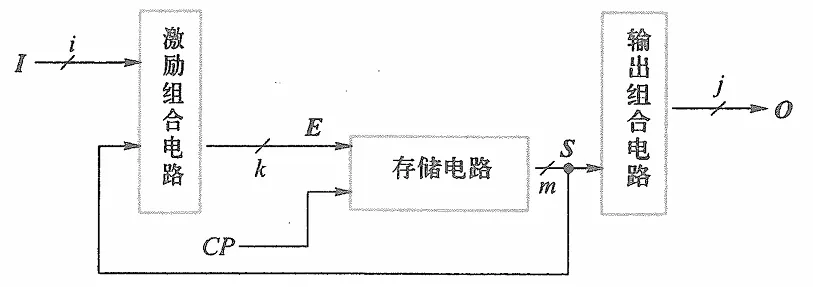

穆尔型电路的输出信号只取决于各触发器的状态,与输入信号没有直接联系

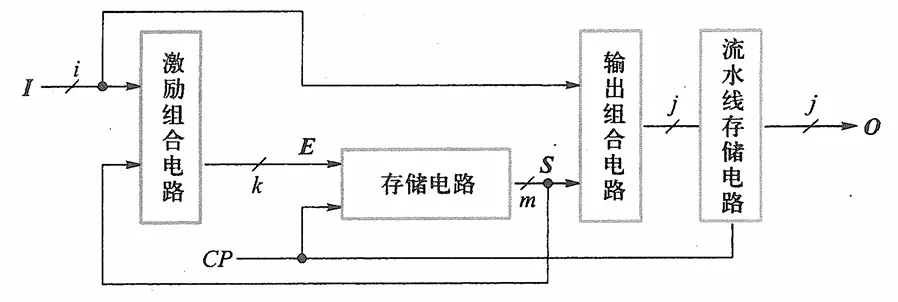

一个将米利型电路转化为穆尔型的方法是流水线输出

不过输出信号会延后一个时钟周期

状态转换

- 由激励组合电路可以写出触发器的激励方程组

- 将激励方程组代入触发器的特性方程得到状态转换方程组

- 由输出组合电路得到输出方程组

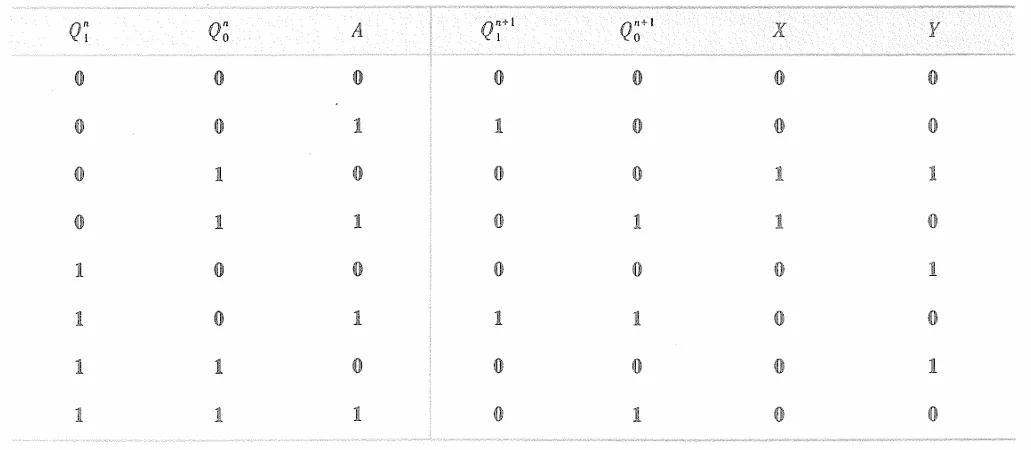

- 由上面三个方程组可以得到状态转换真值表,就像这样

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

目录