目录

CMOS反相器

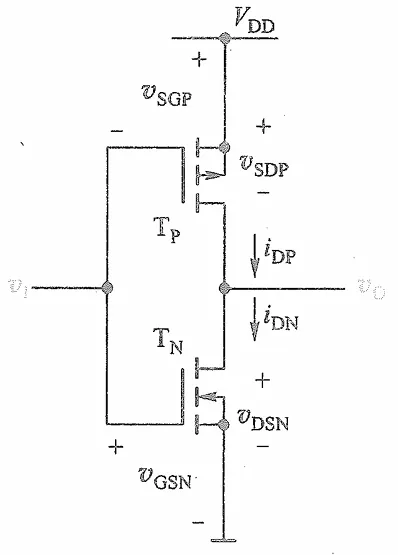

CMOS反相器的结构

CMOS反相器由一个PMOS和一个NMOS组成

其中NMOS的源极s接地,PMOS的源极s接正高压

CMOS反相器的原理

- 如果输入为高电平,即,对于NMOS而言,自然大于临界电压(正),那么NMOS导通;同时对于PMOS而言也高于临界电压(负),那么PMOS关断。这样,输出为低电平

- 如果输入为低电平,即,对于NMOS而言,自然小于临界电压(正),那么NMOS关断;同时对于PMOS而言低于于临界电压(负),那么PMOS导通。这样,输出为高电平

由于只提供栅极电压,实际上并不导通;而反相器输出低电平时,PMOS关断自然没有电流,NMOS漏极输出电压为,源极接地,其电压也为,流过它的电流为。可见当输出电压为零时反相器的功耗极低

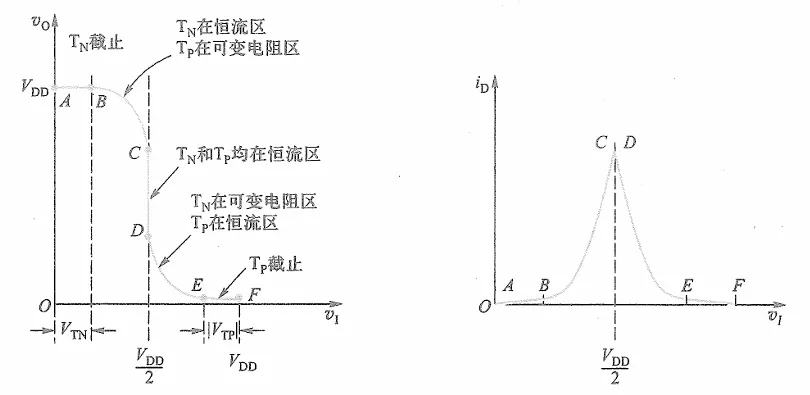

反相器的传输特性

反相器的电压传输特性是指输出电压与输出电压的关系,电流传输特性是指漏极电流(即由一个漏极流到另一个漏极之间的电流,并不是输出电流)。可以画图如下

定义CMOS反相器的阈值电压为

输入电压在阈值电压附近时,漏极电流较大,需要避免反相器长时间工作在这种状态

CMOS与非门和或非门

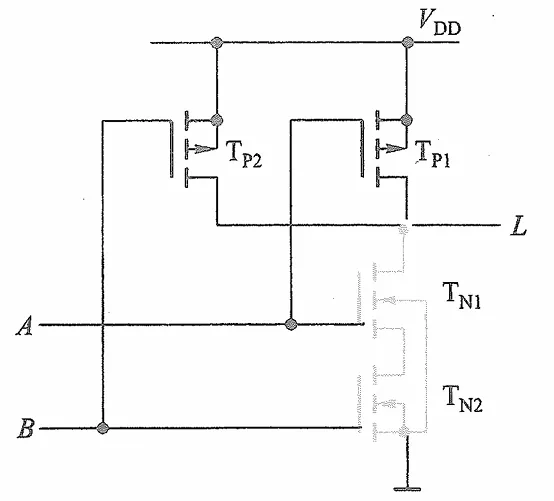

CMOS与非门

CMOS与非门可以画出如下

它的工作原理可以这样描述

- 两个并联决定当AB存在一个是低电平时,其中一个导通,输出为高电平

- 两个串联的决定当都为高电平时,它们都导通,输出为低电平

需要个输入时,只需要将串联的NMOS数目和并联的PMOS数目都变为即可,不过这样会使得导通时的电阻增大

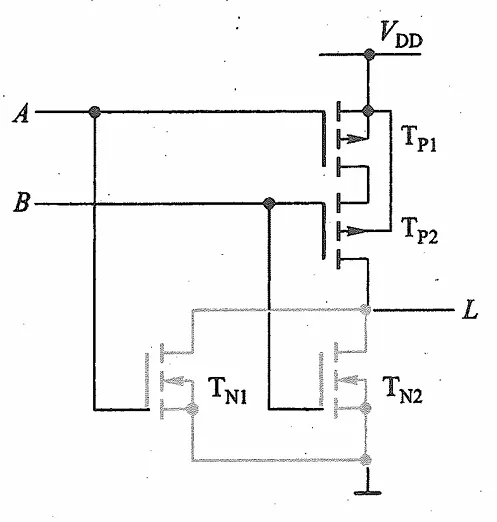

CMOS或非门

CMOS或非门可以画出如下

它的工作原理和与非门相近,不过将PMOS改为了串联,NMOS改为了并联,因而只有AB都为低电平时它才输出高电平

需要个输入时,同样只需要将串联的NMOS数目和并联的PMOS数目都变为

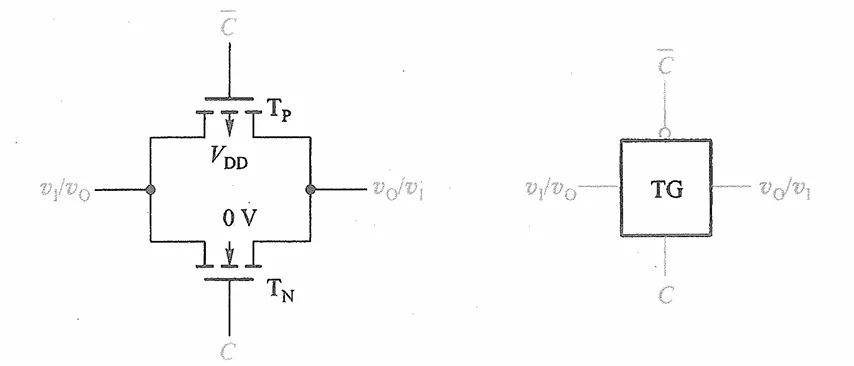

CMOS传输门

CMOS传输门的结构如左图,其符号为右图

右图上方的小圆圈代表0有效,也就是该脚被置为低电平时激活传输门

传输门的原理应当非常显然,在此不多赘述。之所以用两个MOS管,是因为一管越是导通,另一管就越是阻断,这样两个互补的管子并联在一起使得总的电阻变化较小

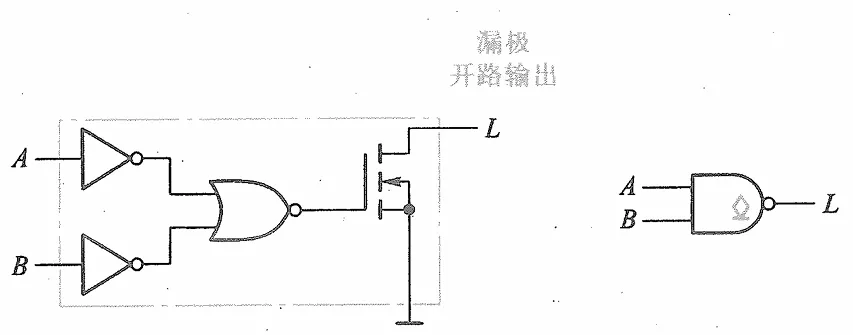

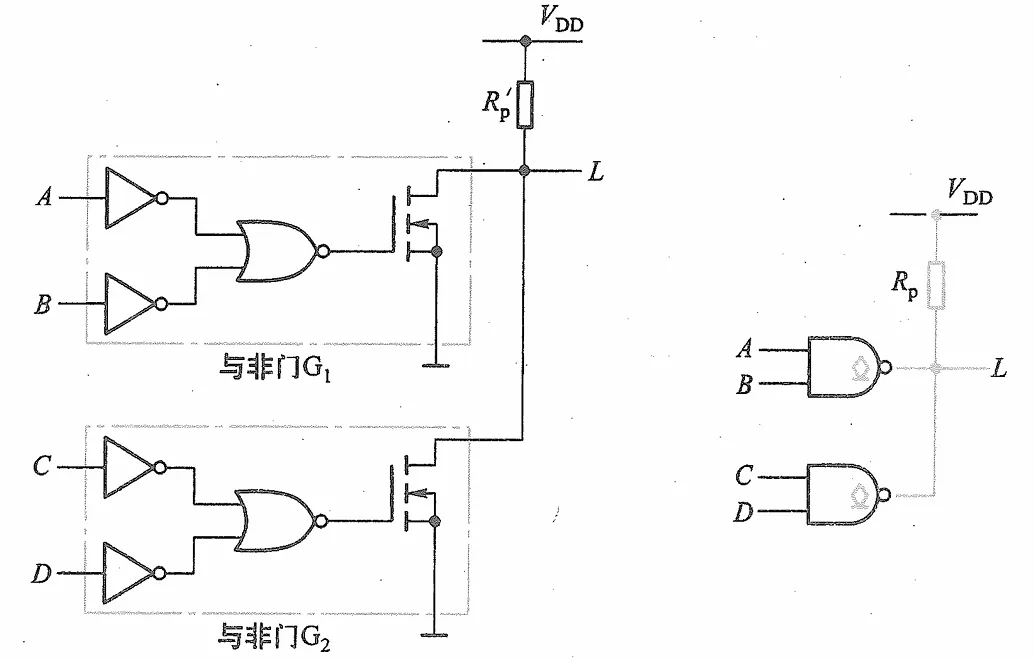

漏极开路门(OD门)

OD门是一种“修饰”,当某个逻辑门被称作OD门时,意味着当它输出高电平时,它实际处于高阻态,需要一个上拉电阻接到电源上才会正常输出高电平。实现OD门只需要加一个MOS管,一个OD与非门的例子是这样的

由于它输出高电平处于高阻态,可以将很多个这样的门并联在一起,实现线与

如果是普通的与非门,当它们输出一个高电平和低电平时,功耗会相当大;而对于OD门而言,只要有一个OD门输出低电平,输出电压就会被它拉低至低电平,其他的OD门都在高阻态,并不输出电流,因而功耗小

因此OD门可以驱动大电流负载(因为电流不是由OD门输出的),或者实现逻辑电平变换(只要接上一个不一样的就行了

不过这个上拉电阻的选择也有讲究

- 并联的OD门只有一个导通,输出低电平,电阻上的电流和外来的输入电流全部进入某个OD门内,它不应超过OD门的最大输入电流,由此给出下拉电阻的最小值

- 并联的OD门都关断,输出高电平,每个OD门都有漏电流,它们与输出电流一起使得电阻上出现压降,此时输出电压不应低于高电平的阈值,由此给出上拉电阻的最大值

实际情况下,如果要求电路速度快,则电阻阻值尽量小;若要求电路功耗小,则阻值尽量大

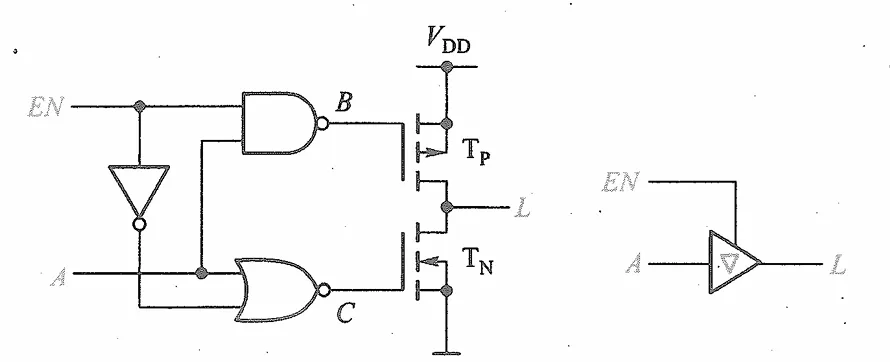

三态门

由于上拉电阻的存在,OD门的速度受限。三态门处理输出高低电平,还可以处于高阻态,这由势能控制。下图是高电平使能三态输出缓冲器的结构和符号

当使能EN被置为低电平时,会使得,两个MOS管都关断,处于高阻态;而EN为高电平时,输出跟随输入变化

CMOS电路的参数

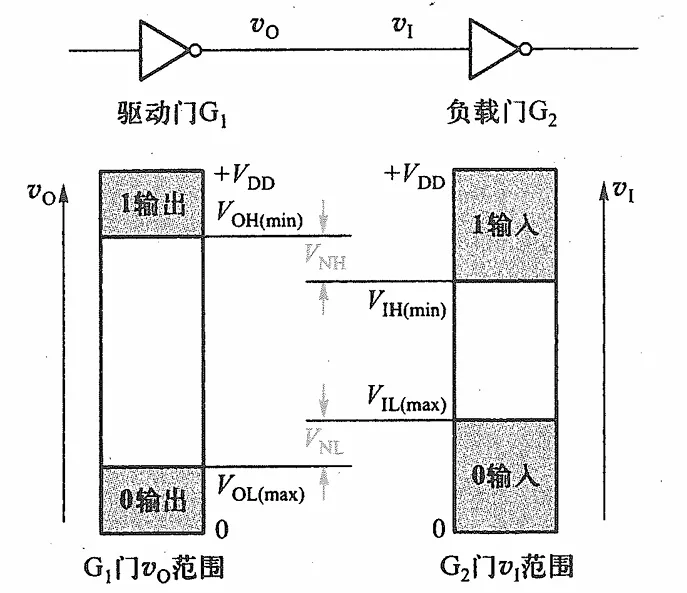

电压限与噪声限

输入输入的高低电平都应有一定的范围

噪声限是门电路中间级之间允许的扰动范围。是高电平允许被减小的量,是低电平允许被增大的量,如图

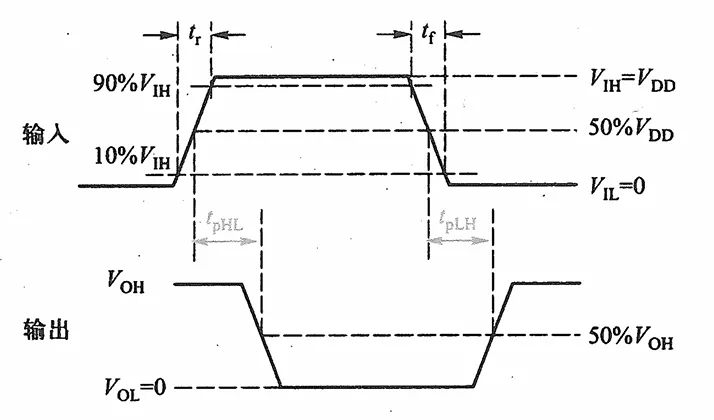

传输延迟时间

传输延迟时间是指输入电压跳变中点与输出电压跳变中点之间的时间差。输入从低跳高的延迟称为,由高跳低的延迟称为。由于CMOS电路的对称性,它们一般相等

对于同一电路而言,传输延迟与电源电压成负相关,与负载电容正相关。平均延迟是低跳高与高跳低延迟的平均值,记为

功耗

CMOS电路的静态功耗很小,功耗来源于动态功耗,即电路状态转换时的功耗。动态功耗有两种来源

- 转换瞬间电流流经MOS管产生的功耗,可以计算如下

其中为功耗电容,是由门电路自身计算得到的等效参数,它与电源电压和工作频率也相关;是输出信号的转换频率

- 电容性负载在高低电平转换时充放电产生的功耗,可以类似计算

其中是负载电容

功耗是这两个功耗的和

可见CMOS电路的功耗正比于频率和电源电压的平方

延时-功耗积

鉴于功耗与频率也就是延迟的倒数成正比,那么可以定义延时-功耗积

它越小就表明电路越接近理想情况

扇入扇出数

可以定义扇入扇出数

- 扇入数是电路输入端的数目

- 扇出数是电路能带同类门电路的最大数目

扇入数是简单的,考虑扇出数的计算。当电路输出高电平时,电流会由驱动门输出。输出电流太大会使得输出电压下降,因而它有最大值。由于它的负载是另一些自己,输入为高电平时,电流会流入负载门,输入电流应当是固定的。那么输出高电平的扇出数就有公式

同样,当输出低电平时,输出电流太大会使得输出电压上升,由此给出输出低电平时的扇出数

该公式未考虑电容性负载,因此工作频率增大时应减小扇出数

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!