请注意,本文编写于 445 天前,最后修改于 406 天前,其中某些信息可能已经过时。

目录

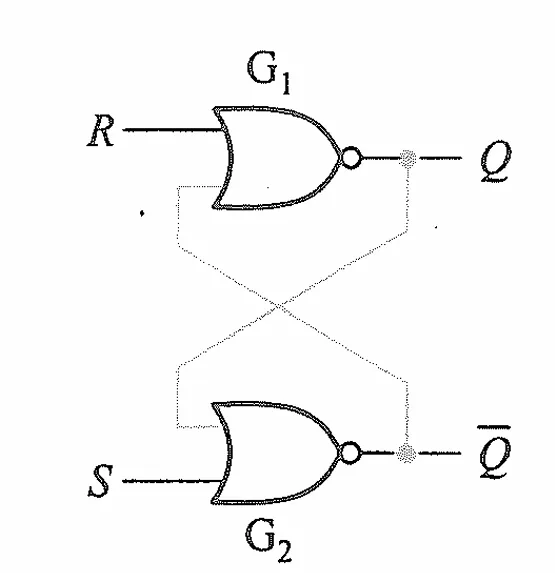

SR锁存器

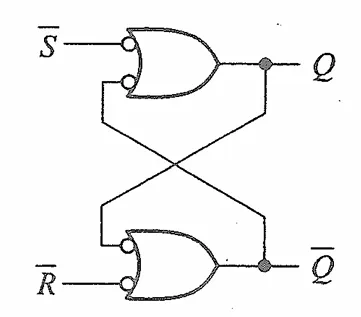

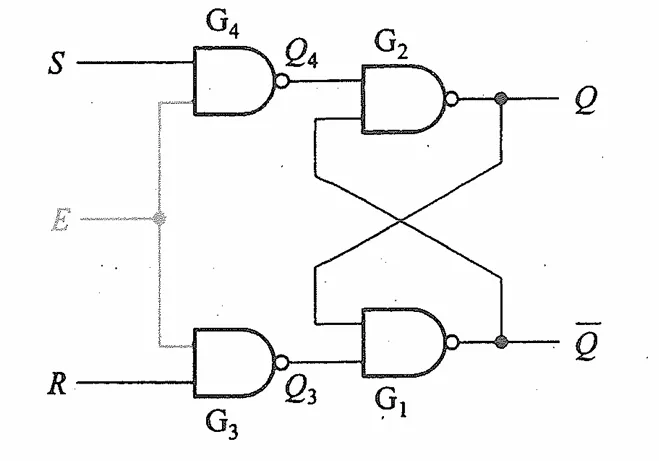

用与非门实现SR锁存器如下

注意到当时,有

这意味着表征了它的状态,当时,状态不变。称为置1端(set),称为置0端(reset)

note

置0端为高电平时将置0,置1端为高电平时将置为1

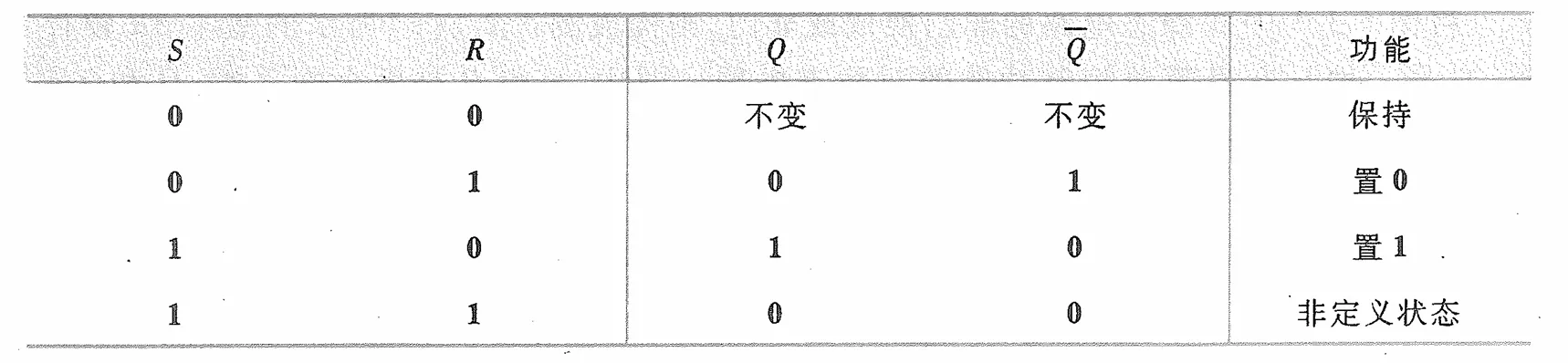

可以画出或非门SR锁存器的功能表

需要注意的是当时,按照或非门的逻辑特性有

这显然是不可以的,如果和同时跳为,那么的状态将不可知。因而SR锁存器有一个禁忌

注意

不可以将SR锁存器的引脚和引脚同时置为1

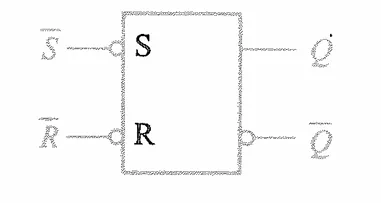

或非门SR锁存器的逻辑符号如下

输出引脚上的小圈圈表示0有效,即当为时引脚输出为

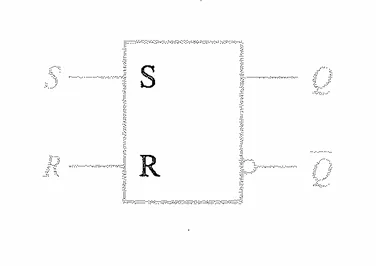

SR锁存器除了可以使用或非门,也可以使用与非门

不过鉴于

它实际上相当于

它的逻辑符号就可以简写为

左侧的小圈圈表示0有效,即引脚输入为0时将置为1,引脚为0时将置为0。如果需要使得为1时置1,引脚应当输入

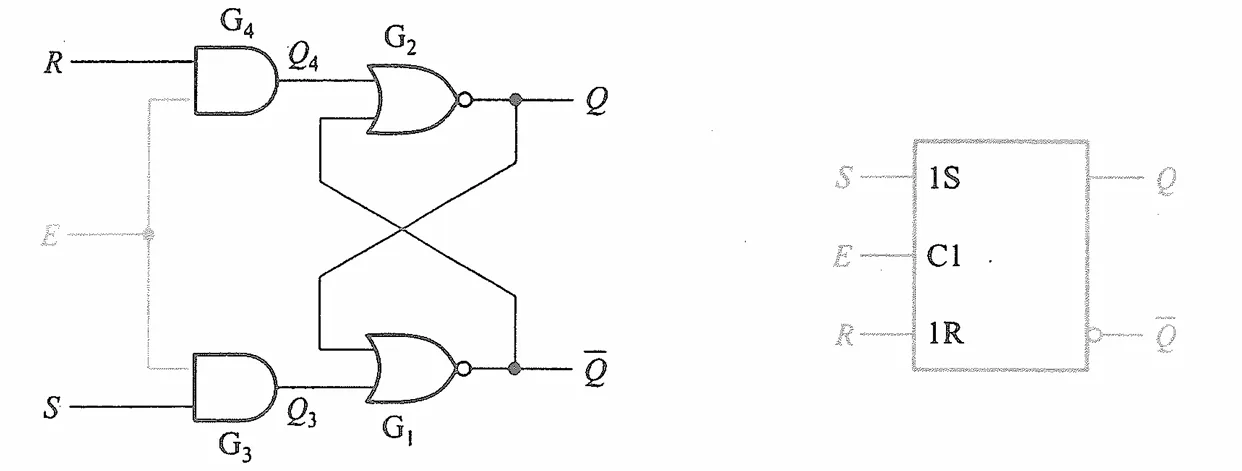

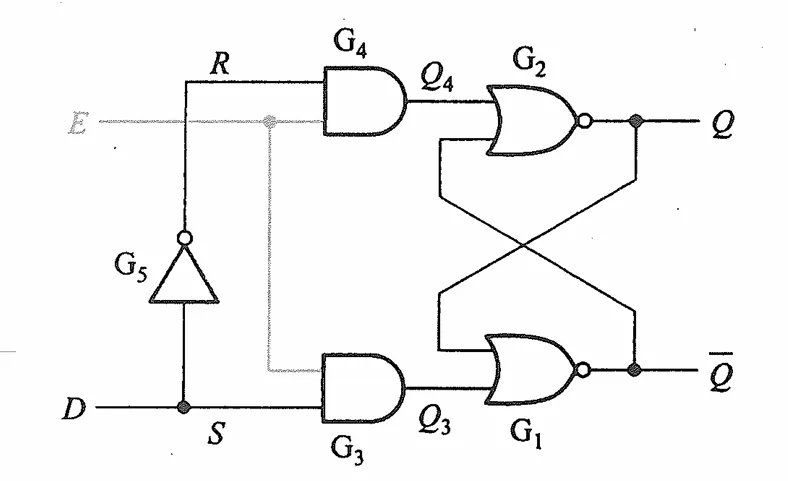

门控SR锁存器

门控SR锁存器添加了使能端,只有当使能端为高电平时才使得输入有效。门控SR锁存器的电路和逻辑符号如下

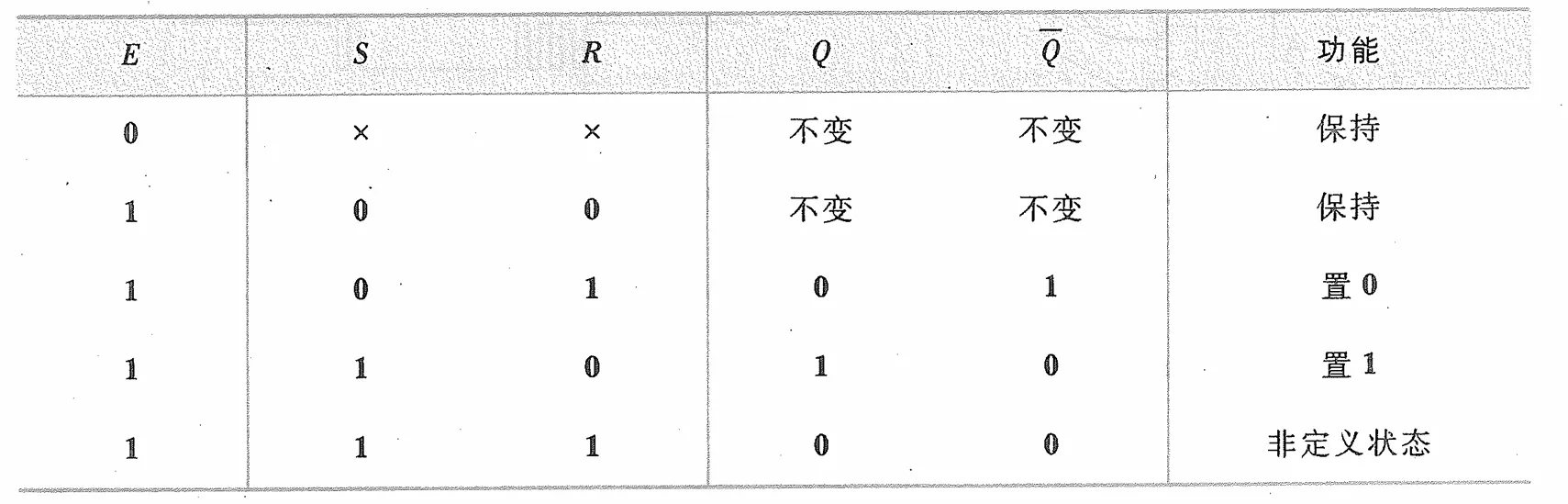

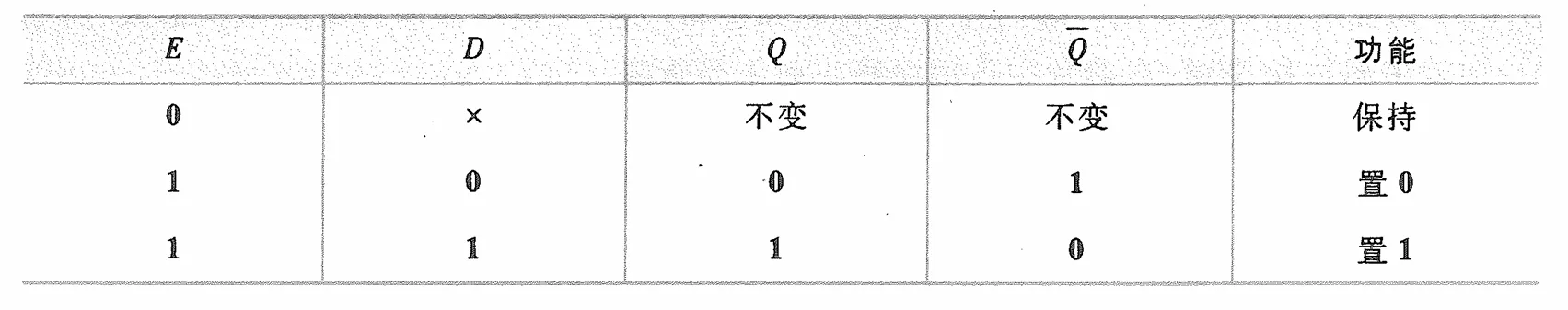

它的功能表如下

也可以使用与非门构建,电路图如下

根据前文所述,由于进行了取反,S和R的位置与或非门的相反

D锁存器

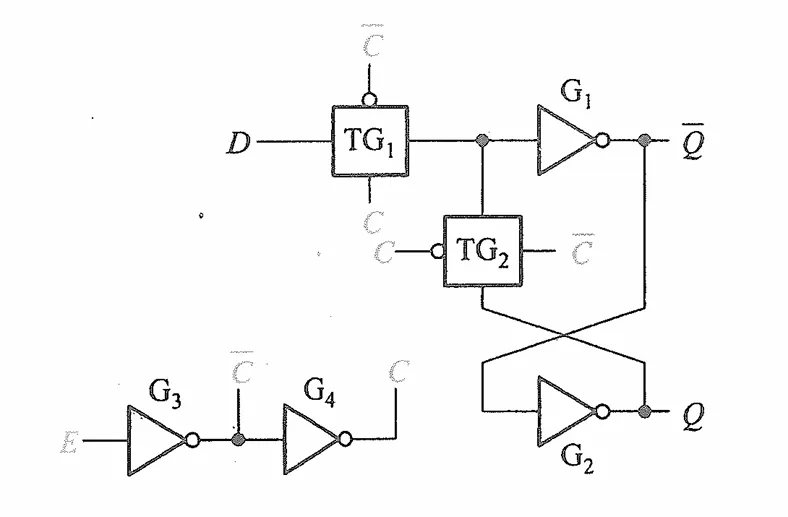

D锁存器使用了一个D引脚代替了SR引脚控制置1和置0,另有使能信号控制是否保持状态。D锁存器可以由传输门构建也可以由逻辑门构建

需要注意的是,建立时间 保持时间 脉冲宽度

note

D的逻辑电平需要在使能E的有效电平结束前一段时间()建立,需要在E的的有效电平结束后保持一段时间(),为了使Q正确的置为D,使能信号E需要保持一段时间()

事实上输出Q相对于D和E也存在延迟,不过它们的延迟相差不大。但是Q从0跳1与从1跳0的延迟具有差异,记为

一般取其平均延迟

本文作者:GBwater

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

目录